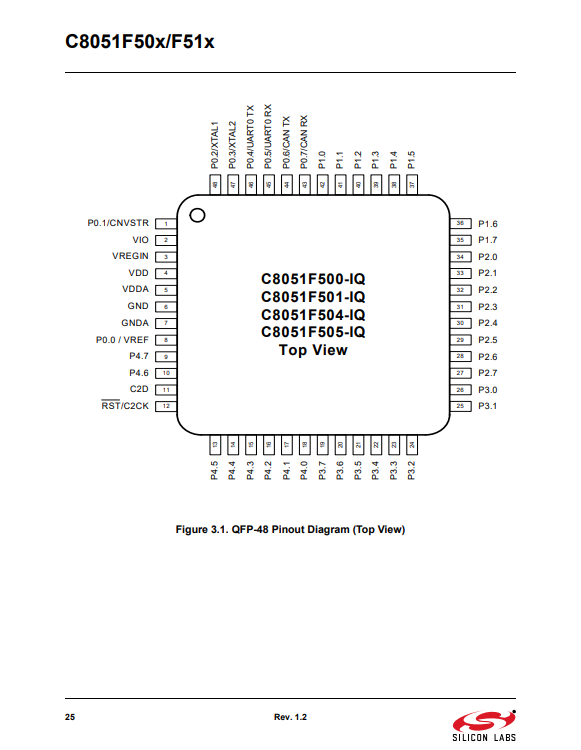

C8051F500-IQR IC MCU 8BIT 64KB FLASH 48TQFP

Paramedr Cynnyrch

Disgrifiad

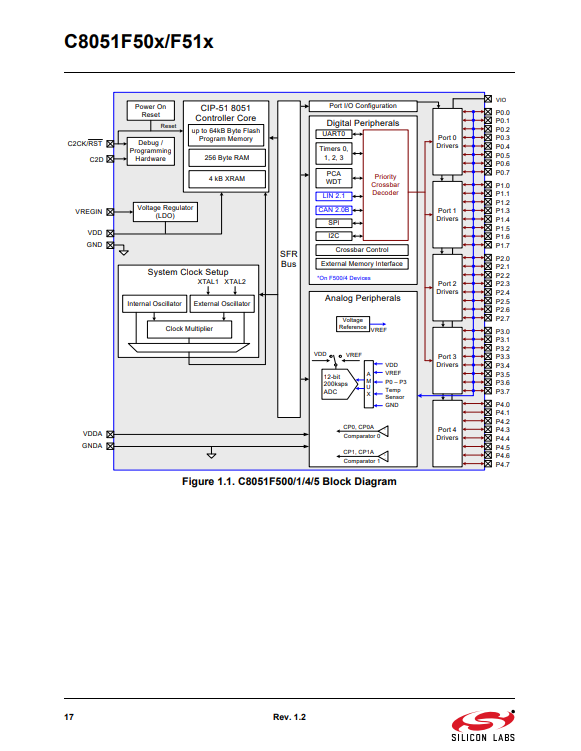

Gyda Rheoleiddiwr Foltedd ar-sglodion, Power-On Reset, monitor VDD, Watchdog Timer, ac osgiliadur cloc, mae'r dyfeisiau C8051F50x / F51x yn ddatrysiadau System-ar-a-Chip sy'n wirioneddol annibynnol.Gellir ail-raglennu'r cof Flash hyd yn oed o fewn cylched, gan ddarparu storfa ddata nad yw'n anweddol, a hefyd yn caniatáu uwchraddio maes y firmware 8051.Mae gan feddalwedd defnyddwyr reolaeth lwyr ar bob perifferolion, a gallant gau unrhyw perifferolion neu bob un ohonynt yn unigol er mwyn arbed pŵer.Mae Rhyngwyneb Datblygu 2-Wire (C2) Silicon Labs ar sglodion yn caniatáu anymwthiol (yn defnyddio dim adnoddau ar sglodion), cyflymder llawn, difa chwilod mewn cylched gan ddefnyddio'r MCU cynhyrchu a osodwyd yn y cais terfynol.Mae'r rhesymeg dadfygio hon yn cefnogi archwilio ac addasu cof a chofrestrau, gosod torbwyntiau, camu sengl, gorchmynion rhedeg a stopio.Mae pob perifferolion analog a digidol yn gwbl weithredol wrth ddadfygio gan ddefnyddio C2.Gellir rhannu'r ddau bin rhyngwyneb C2 â swyddogaethau defnyddwyr, gan ganiatáu dadfygio yn y system heb feddiannu pinnau pecyn.

| Manylebau: | |

| Priodoledd | Gwerth |

| Categori | Cylchedau Integredig (ICs) |

| Embedded - Microreolyddion | |

| Mfr | Labs Silicon |

| Cyfres | C8051F50x |

| Pecyn | Tâp a Rîl (TR) |

| Tâp Torri (CT) | |

| Digi-Reel® | |

| Statws Rhan | Actif |

| Prosesydd Craidd | 8051 |

| Maint Craidd | 8-Did |

| Cyflymder | 50MHz |

| Cysylltedd | EBI/EMI, SMBus (2-Wire/I²C), CANbus, LINbus, SPI, UART/USART |

| Perifferolion | POR, PWM, Synhwyrydd Temp, WDT |

| Nifer yr I/O | 40 |

| Maint Cof Rhaglen | 64KB (64K x 8) |

| Math Cof Rhaglen | FFLACH |

| Maint EEPROM | - |

| Maint RAM | 4.25K x 8 |

| Foltedd - Cyflenwad (Vcc/Vdd) | 1.8V ~ 5.25V |

| Trawsnewidyddion Data | A/D 32x12b |

| Math Osgiliadur | Mewnol |

| Tymheredd Gweithredu | -40°C ~ 125°C (TA) |

| Math Mowntio | Mount Wyneb |

| Pecyn / Achos | 48-TQFP |

| Pecyn Dyfais Cyflenwr | 48-TQFP (7x7) |

| Rhif Cynnyrch Sylfaenol | C8051F500 |

CysylltiedigCYNHYRCHION

-

Ffon

-

E-bost

-

skype

-

whatsapp

whatsapp