EP1C6Q240C8N IC FPGA 185 I/O 240QFP

Paramedr Cynnyrch

Disgrifiad

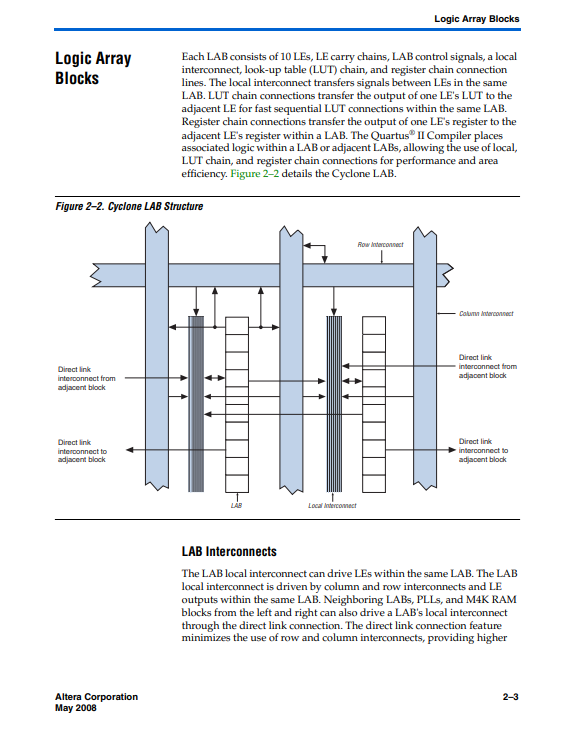

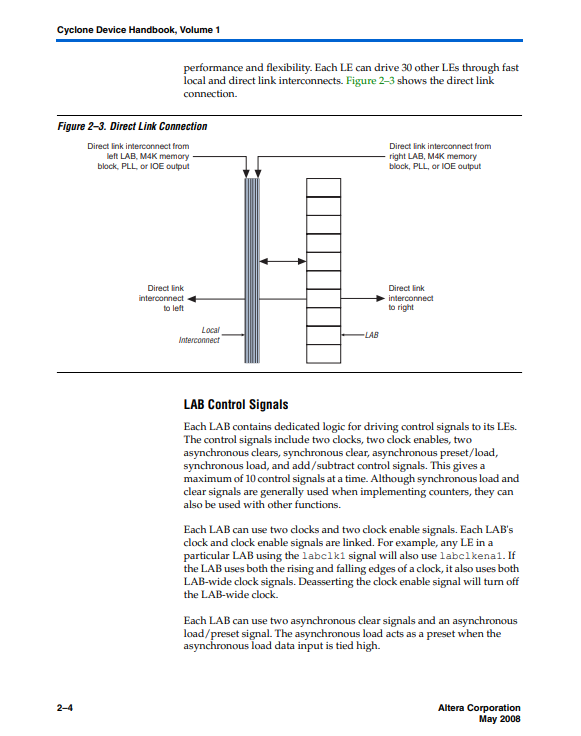

Mae dyfeisiau Cyclone® yn cynnwys pensaernïaeth dau-ddimensiwn yn seiliedig ar resi a cholofnau i weithredu rhesymeg arferiad.Mae rhyng-gysylltiadau colofn a rhes o gyflymderau amrywiol yn darparu rhyng-gysylltiadau signal rhwng LABs a blociau cof wedi'u mewnosod.Mae'r arae rhesymeg yn cynnwys LABs, gyda 10 LE ym mhob LAB.Mae LE yn uned fach o resymeg sy'n darparu gweithrediad effeithlon o swyddogaethau rhesymeg defnyddwyr.Mae LABs wedi'u grwpio'n rhesi a cholofnau ar draws y ddyfais.Mae dyfeisiau seiclon yn amrywio rhwng 2,910 ac 20,060 LEs.Mae blociau RAM M4K yn wir flociau cof porthladd deuol gyda darnau 4K o gof ynghyd â chydraddoldeb (4,608 bits).Mae'r blociau hyn yn darparu cof porthladd deuol gwirioneddol pwrpasol, porthladd deuol syml, neu gof un porthladd hyd at 36-bits o led hyd at 250 MHz.Mae'r blociau hyn wedi'u grwpio'n golofnau ar draws y ddyfais rhwng rhai LABs.Mae dyfeisiau seiclon yn cynnig rhwng 60 a 288 Kbits o RAM wedi'i fewnosod.Mae pob pin I/O dyfais Seiclon yn cael ei fwydo gan elfen I/O (IOE) sydd wedi'i lleoli ar ben rhesi a cholofnau LAB o amgylch ymylon y ddyfais.Mae pinnau I / O yn cefnogi amrywiol safonau I / O un pen a gwahaniaethol, megis y safon PCI 66- a 33-MHz, 64- a 32-did a safon I / O LVDS hyd at 640 Mbps.Mae pob IOE yn cynnwys byffer I/O deugyfeiriadol a thair cofrestr ar gyfer cofrestru signalau mewnbwn, allbwn ac allbwn.Mae pinnau DQS, DQ, a DM pwrpas deuol ynghyd â chadwyni oedi (a ddefnyddir i alinio signalau DDR fesul cam) yn darparu cefnogaeth rhyngwyneb gyda dyfeisiau cof allanol fel DDR SDRAM, a dyfeisiau FCRAM hyd at 133 MHz (266 Mbps).Mae dyfeisiau seiclon yn darparu rhwydwaith cloc byd-eang a hyd at ddau PLL.Mae'r rhwydwaith cloc byd-eang yn cynnwys wyth llinell cloc byd-eang sy'n gyrru trwy'r ddyfais gyfan.Gall y rhwydwaith cloc byd-eang ddarparu clociau ar gyfer yr holl adnoddau o fewn y ddyfais, megis IOEs, LEs, a blociau cof.Gellir defnyddio'r llinellau cloc byd-eang hefyd ar gyfer signalau rheoli.Mae PLLs seiclon yn darparu clocio pwrpas cyffredinol gyda lluosi cloc a symud cyfnodau yn ogystal ag allbynnau allanol ar gyfer cefnogaeth I / O gwahaniaethol cyflym.

| Manylebau: | |

| Priodoledd | Gwerth |

| Categori | Cylchedau Integredig (ICs) |

| Wedi'i fewnosod - FPGAs (Arae Gât Rhaglenadwy Maes) | |

| Mfr | Intel |

| Cyfres | Seiclon® |

| Pecyn | Hambwrdd |

| Statws Rhan | Darfodedig |

| Nifer y LABs/CLBs | 598 |

| Nifer yr Elfennau Rhesymeg/Celloedd | 5980 |

| Cyfanswm Darnau RAM | 92160 |

| Nifer yr I/O | 185 |

| Foltedd - Cyflenwad | 1.425V ~ 1.575V |

| Math Mowntio | Mount Wyneb |

| Tymheredd Gweithredu | 0°C ~ 85°C (TJ) |

| Pecyn / Achos | 240-BFQFP |

| Pecyn Dyfais Cyflenwr | 240-PQFP (32x32) |

| Rhif Cynnyrch Sylfaenol | EP1C6 |

CysylltiedigCYNHYRCHION

-

Ffon

-

E-bost

-

skype

-

whatsapp

whatsapp